DC-DC常见应用问题解疑(一)

对于在工程师选型、测试的时候常会遇到的电源管理芯片问题,本期SCT做了归纳和整理,方便快速解答大家的疑惑。欢迎各位专家在留言区补充讨论问答。

目录

1 静态电流IQ,为什么单板上实测值与芯片规格书标称值不一样?

2 PSM(PFM)、USM、FPWM(FCCM)差别及优缺点?为什么有的DCDC存在电感啸叫现象?

3 芯片Vin_UVLO含义

4 EN使能设计逻辑,如何规避上下电回勾震荡问题?

5 Soft-start软启动,解决上电过冲超调、电子负载重载无法启机等问题

6 如何理解热阻参数和通过热阻计算芯片结温?

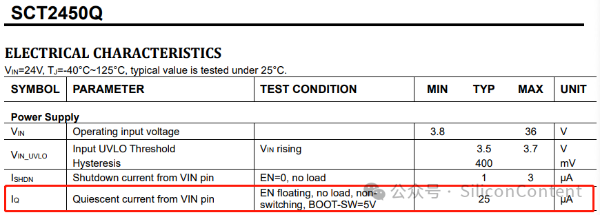

一、静态电流IQ,为什么单板上实测值与芯片规格书标称值不一样?

静态电流IQ规格书标称值,是针对芯片单体进行测试和定义。是芯片内部MOS不工作(non-switching状态)、只有芯片逻辑电路处于待机状态时的值。

单板上,芯片正常工作起来后,芯片内部MOS正常开关(switching)存在开关损耗和驱动损耗、外围器件如电感、EN管脚分压电阻、FB反馈电阻均会有损耗。

因此单板上即使在无负载情况下,静态电流也会大于芯片规格书定义的值。

以SCT2450Q为例,芯片IQ为25uA,demo板上电后电路工作起来的空载输入电流约80uA。

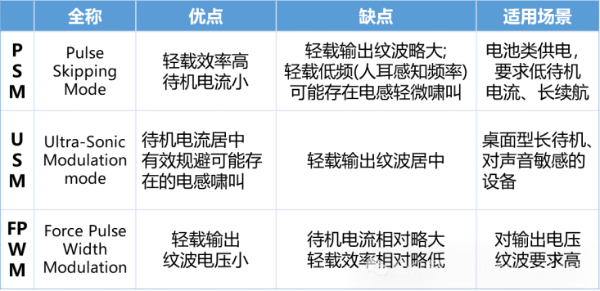

二、PSM(PFM)、USM、FPWM(FCCM)差别及优缺点?为什么有的DCDC存在电感啸叫现象?

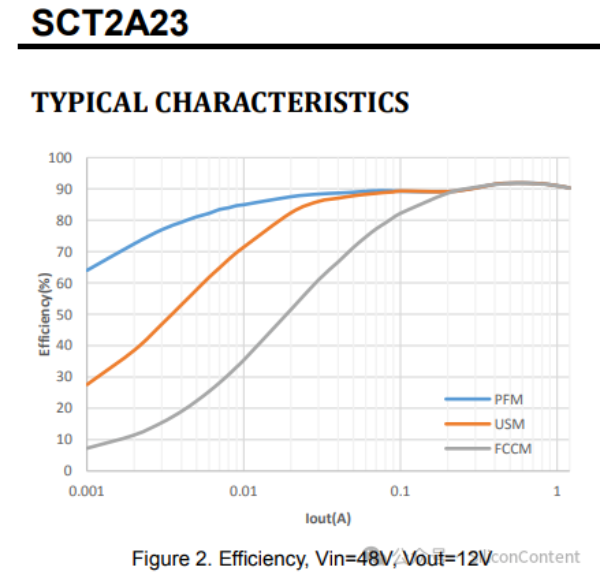

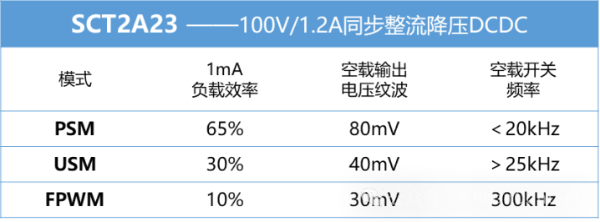

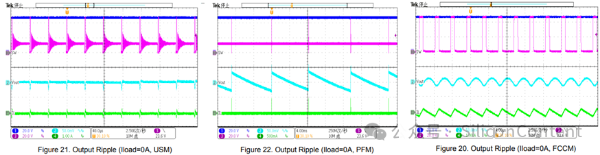

以SCT2A23 (100V/ 1.2A同步整流)为例,三种工作模式可选择,不同工作模式差异如图

以SCT2A23 (100V/ 1.2A同步整流)为例,三种工作模式可选择,不同工作模式差异如图

三、芯片Vin_UVLO含义

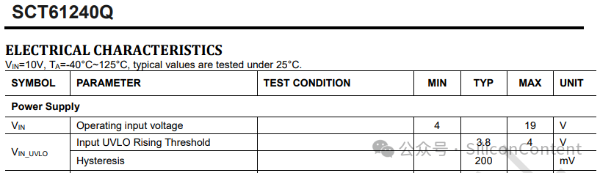

UVLO Rising Threshold即芯片启动电压,即当输入电压上升到这个电压值时芯片启动工作;

Hysteresis即回差,即当芯片正常启动工作后,如果输入电压跌落到VULO_Rising-Hysteresis时芯片停止工作。

如SCT61240Q,Rising电压3.8V、回差0.2V,即芯片启动电压(Von)3.8V,芯片关机电压(Voff)3.6V。

四、EN使能设计逻辑,如何规避上下电回勾震荡问题?

EN主要用作芯片使能控制,在输入电压≥UVLO电压时,可通过EN控制芯片上下电;同时可设置启动电压(Von)和关机电压(Voff)回差,确保任何情况下芯片不会因为在启机临界点电压附近出现误开关问题。有效解决下电过程因负载释放引起的电压回勾、震荡问题。

EN设计逻辑:

1.Vout>UVLO,通过EN设置的Voff电压>Vout;

2.Vout<UVLO,通过EN设置的Voff电压>UVLO;

3.Vhys>芯片Vin_UVLO_Hysteresis;

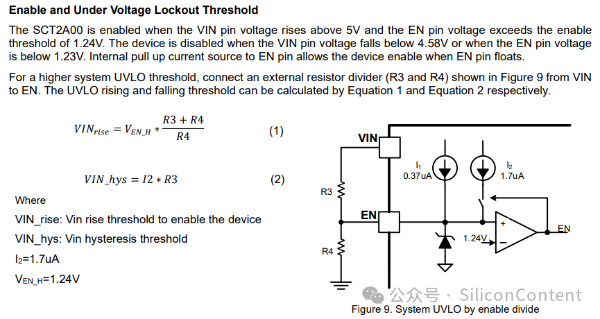

以SCT2A00(100V/0.6A DC-DC)为例,通过EN设置Von、Voff计算公式如下

根据计算公式:EN上拉电阻越大则回差越大,越不容易因为输入电压的回勾导致芯片反复重启;EN对地电阻阻值选择建议小于Vin_fall/(I1+I2);

五、Soft-start软启动,解决上电过冲超调、电子负载重载无法启机等问题

什么是软启动

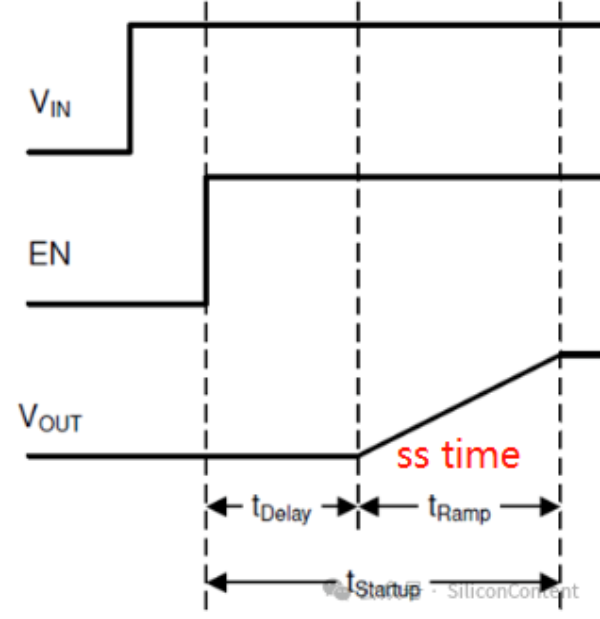

SS软启动(Soft-start)是为开关电源电路配置一个启动时间,在启动后能够使输出电压单调上升到目标电压值。

软启动时间SS time即输出电压从开始启动至启动结束的时间。

软启动作用

降低冲击电流:有效抑制浪涌电流,避免在启动瞬间对输出电容充电的电流达到开关电源的限值而触发保护;

通常电子负载带载上电、输出有大容量电容时,由于线性度较差,上电时形成较大冲击电流,同时电压建立给输出大电容充电,叠加后在输出电压建立过程中形成大负载电流,容易触发芯片过流保护而无法上电。

解决反复重启问题:减小对开关电路本身以及后端负载的电流应力,减小输出瞬态负载电流反应到输入端,使输入电压跌落导致的芯片反复重启。

解决过冲、抖动:SS功能利于输出电压“单调上升”,而不会出现抖动或上电速率太快出现电压过冲超调。

这对上电时序有较高要求的数字器件尤其是FPGA类器件更加重要,避免导致后端数字器件或FPGA器件发生闩锁效应(Latch-up)问题。

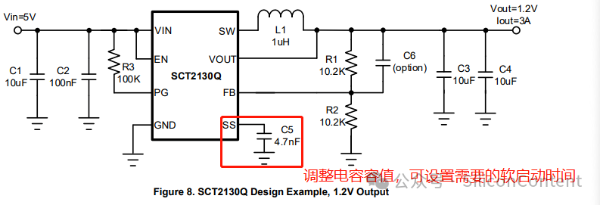

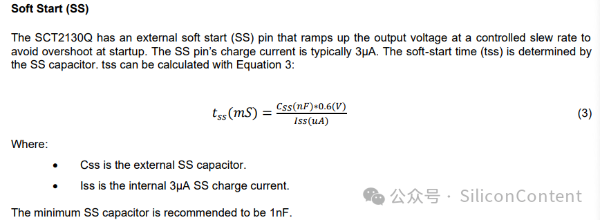

软启动电容&时间选择

根据应用选择合适的值,并不是电容越大、软启时间越长越好。电容越大则放电时间越长,若存在快速反复上下电场景,因软启动电容未完全放电,在重新上电时不走软启动流程,可能导致输出电压出现过冲等现象。

六、如何理解热阻参数和通过热阻计算芯片结温?

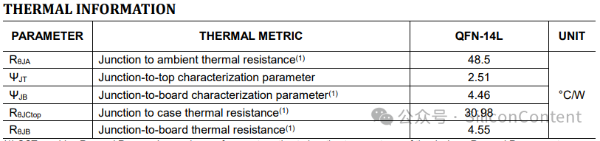

下表是SCT2464Q(40V/6A BUCK, QFNFC4×3.5-14L Package)的典型热指标

RθJA

定义:静止空气条件下结对环境的热阻,热量通过封装体传导,与PCB的关系小,如一些立式封装的产品。

适用性:用于比较相同封装类型下不同器件的热性能,不适合用于结温估算。

RθJC

定义:结与外壳表面(顶部或底部封装)的热阻,所有的热量都通过器件的单表面(壳体顶部或封装底部)传导。

适用性:适用于仅在封装顶部或底部安装散热片的情况,其中90%以上的热量从顶部或底部散热。

对于没有顶部散热的典型塑料封装SMD器件,仅通过测量外壳顶部温度和计算器件功耗来估算结温是不正确的,这可能导致估算的值比实际结温高得多。

RθJB

定义:结到PCB(不是封装底部)的热阻,PCB是器件散热的主要路径,确保所有的热量都流向PCB。

适用性:JEDEC标准:FR4、4层、1.6mm厚的高导热PCB(High-KPCB)评估,顶层和底层铜箔厚度2oz,中间两层1oz;单板尺寸通常为11.4×7.6cm或11.4×10.2。

如果实际应用中的PCB设计类似或更优化,则可使用此参数估算结温,TJ=TB+(θJB*P)。

ΨJT/ΨJB

定义:热特性参数,表示芯片结与参考点之间的温度差与总耗散功率的比值,

适用性:在实际应用中,热传导路径是多种多样的,热量通过多个通道传导,热特性参数Ψ表示芯片结与参考点之间的温度差与总耗散功率的比值,更适合于估算结温且更加准确,常用的结温计算方式:TJ=TC+(ΨJT*P)。

期待交流