# Quad Channel Power Management IC for Ultra Compact Camera Module

# **FEATURES**

- Wide Input Voltage Range: 4V-19V

- Synchronous HV Pre-Buck1:

- Up to 1.2A Continuous Output Current

- Auto-adaptive Output Voltage Depends on LDO

Output Voltage

- Synchronous LV Post-Buck2:

- Powered by Pre-Buck1

- Up to 0.6A Continuous Output Current

- Fixed Output Voltage of 1.8V

- Synchronous LV Post-Buck3:

- Powered by Pre-Buck1

- Up to 1.2A Continuous Output Current

- Adjustable Output Voltage: 1.1V/1.2V/1.3V/1.5V

- LV Post-LDO:

- Powered by Pre-Buck1

- Up to 0.3A Continuous Output Current

- Adjustable Output Voltage: 2.7V/2.8V/2.9V/3.3V

- Low Noise and High PSRR

- Low Shutdown Current: 1uA

- Fixed 2.2MHz Switching Frequency

- Integrated Frequency Dither for EMI Mitigation

- FCCM Operation

- 60ns Minimum On-time

- 6 Flexible Sequence via External Resistor

- 9 Flexible Output Voltage via External Resistor

- Push-pull Power Good Indicator

- Integrated Hiccup Mode Protection Features:

- Input Over-voltage Protection

- Output Over-voltage Protection

- Output Under-voltage Protection

- Over-current Protection

- Adjustable Under-voltage Lockout

- Thermal Shutdown Protection

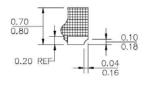

- Available in QFN-18L(2.5mm\*3.5mm)

# APPLICATIONS

- ADAS

- Compact Camera Module

- Cabin Monitor

## DESCRIPTION

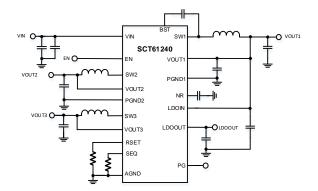

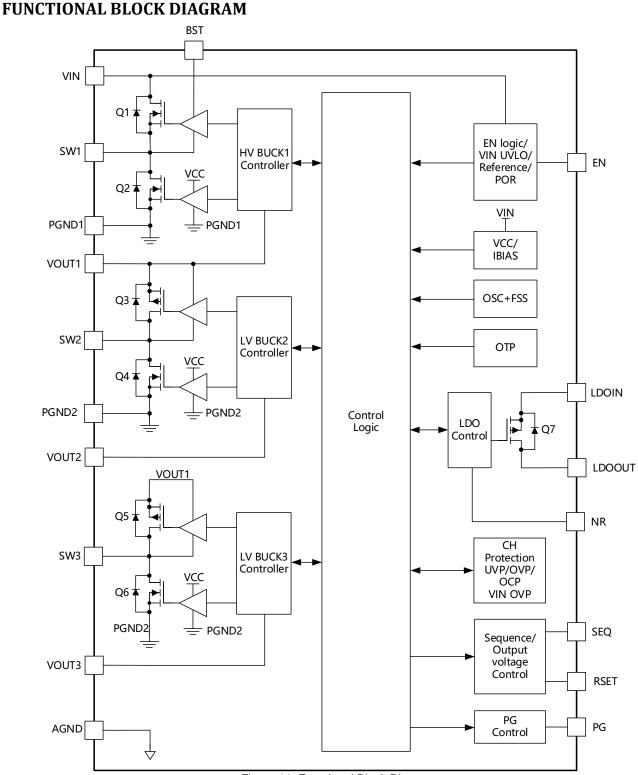

The SCT61240 is a highly integrated power management IC (PMIC) optimized for camera system. It integrates three high efficiency synchronous BUCK converters (HVBUCK1, LVBUCK2, LVBUCK3), and a high-PSRR low noise LDO with OV/UV monitoring on all outputs.

VOUT1 is the output of BUCK1, which is powered from VIN (Power Over Coax) and can output 1.2A continuous current with the output voltage set to LDOOUT+300mV/500mV or fixed 3.3V.

VOUT2 is the output of BUCK2, which is powered from VOUT1 and can output 600mA continuous current with the output voltage fixed to 1.8V.

VOUT3 is the output of BUCK3, which is powered from VOUT1 and can output 1.2A continuous current with the output voltage set to 1.1V/1.2V/1.3V/1.5V through RSET PIN for different sensors.

LDOOUT is the output of LDO, which is powered from VOUT1 (need to connect LDOIN to VOUT1) and can output 300mA continuous current with the output voltage set to 2.7V/2.8V/2.9V/3.3V through RSET PIN for different sensors.

With a compact QFN2.5x3.5 package, the SCT61240 greatly reduces external components count and PCB space.

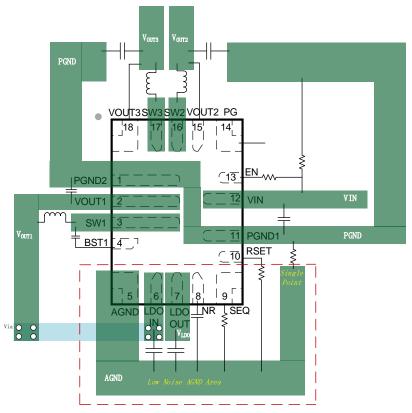

# **TYPICAL APPLICATION**

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version

Revision 1.0: Released to Market

Revision 1.1: Update DEVICE ORDER INFORMATION

## **DEVICE ORDER INFORMATION**

| ORDERABLE<br>DEVICE   | PACKAGI<br>NG TYPE | STANDARD<br>PACK QTY | PACKAGE<br>MARKING | PINS | VOUT1       | PG<br>VOLTAGE | PACKAGE<br>DESCRIPTION |

|-----------------------|--------------------|----------------------|--------------------|------|-------------|---------------|------------------------|

| SCT61240FJCR          | Tape &<br>Reel     | 5000                 | 1240               | 18   | Fixed 3.3V  | 3.3V          | FCTQFN<br>2.5×3.5-18L  |

| SCT61240-<br>0000FJCR | Tape &<br>Reel     | 5000                 | 1240               | 18   | LDOOUT+0.3V | 1.8V          | FCTQFN<br>2.5×3.5-18L  |

| SCT61240-<br>0001FJCR | Tape &<br>Reel     | 5000                 | 1240               | 18   | LDOOUT+0.5V | 1.8V          | FCTQFN<br>2.5×3.5-18L  |

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                          | MIN  | MAX | UNIT |

|--------------------------------------|------|-----|------|

| VIN, EN                              | -0.3 | 24  | V    |

| SW1                                  | -1   | 24  | V    |

| BST-SW1                              | -0.3 | 6   | V    |

| Others                               | -0.3 | 6   | V    |

| Junction temperature <sup>(2)</sup>  | -40  | 150 | °C   |

| Storage temperature T <sub>STG</sub> | -65  | 150 | °C   |

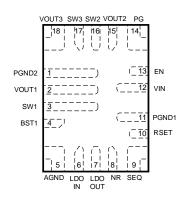

## **PIN CONFIGURATION**

#### Top View: 18-Lead FCTQFN 2.5mmx3.5mm

(1) Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

(2) The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 170°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

## **PIN FUNCTIONS**

| NAME  | NO. | DESCRIPTION                                                                                                                                                                                                            |

|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGND2 | 1   | Power ground for Buck 2 and Buck 3. Should be electrically connected to the system power ground plane with the shortest and lowest-impedance connection possible.                                                      |

| VOUT1 | 2   | Feedback for Buck 1 and power source for Buck 2 and Buck 3. Connect VOUT1 pin to the buck 1 output directly. A decoupling capacitor to ground is recommended to be placed close to VOUT1 to minimize switching spikes. |

| SW1   | 3   | Buck 1 switch node. SW is the output of the internal power switch. Connect to an external inductor using a wide PCB trace.                                                                                             |

| BST   | 4   | Bootstrap capacitor connection pin for HVBuck1. Connect a 0.1µF ceramic capacitor between this pin and SW1.                                                                                                            |

| <b>PIN FUNCTIONS (</b> | continued) |

|------------------------|------------|

|------------------------|------------|

| NAME   | NO. | DESCRIPTION                                                                                                                                                                            |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND   | 5   | Analog ground. AGND is the reference GND for the internal logic and signal circuit. AGND is not internally connected to Power Ground, make sure AGND connected to power ground in PCB. |

| LDOIN  | 6   | Supply voltage input of LDO. Connect a 2.2µF or larger decouple ceramic capacitor between this pin and ground.                                                                         |

| LDOOUT | 7   | LDO output. Connect a 10µF ceramic decouple capacitor between this pin and ground.                                                                                                     |

| NR     | 8   | Noise reduction. Connect a 0.1µF ceramic capacitor between this pin and ground to reduce LDOOUT noise.                                                                                 |

| SEQ    | 9   | Power sequence selection. Connect a resistor between this pin and ground to set the power up sequence. See SEQ setting table.                                                          |

| RSET   | 10  | Output voltage selection for all channels. Connect a resistor between this pin and ground to set the output voltage. See RSET setting table.                                           |

| PGND1  | 11  | Power ground for Buck 1. Should be electrically connected to the system power ground plane with the shortest and lowest-impedance connection possible.                                 |

| VIN    | 12  | Input supply voltage. A decoupling capacitor to ground is recommended to be placed close to VIN to minimize switching spikes.                                                          |

| EN     | 13  | Chip enable. Set EN high to enable the part. EN pin is also a high voltage PIN which can connect to VIN.                                                                               |

| PG     | 14  | Power good indication for all channels. PG output is push-pull, PG at high state indicates all outputs work well.                                                                      |

| VOUT2  | 15  | Feedback for Buck 2. Connect VOUT2 pin to the buck 2 output directly.                                                                                                                  |

| SW2    | 16  | Buck 2 switch node. SW is the output of the internal power switch. Connect to an external inductor using a wide PCB trace.                                                             |

| SW3    | 17  | Buck 3 switch node. SW is the output of the internal power switch. Connect to an external inductor using a wide PCB trace.                                                             |

| VOUT3  | 18  | Feedback for Buck 3. Connect VOUT3 pin to the buck 3 output directly.                                                                                                                  |

# **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range unless otherwise noted

| PARAMETER | DEFINITION                     | MIN | MAX | UNIT |

|-----------|--------------------------------|-----|-----|------|

| Vin       | Input voltage range            | 4   | 19  | V    |

| TJ        | Operating junction temperature | -40 | 125 | °C   |

## **ESD RATINGS**

| PARAMETER | DEFINITION                                  | MIN | МАХ | UNIT |

|-----------|---------------------------------------------|-----|-----|------|

|           | Human Body Model(HBM), per AEC-Q100-002     | -2  | 2   | kV   |

| Vesd      | Charged Device Model(CDM), per AEC-Q100-011 | -1  | 1   | kV   |

# THERMAL INFORMATION

| PARAMETER              | THERMAL METRIC                                           | QFN-18L | UNIT   |

|------------------------|----------------------------------------------------------|---------|--------|

| R <sub>0JA</sub>       | Junction to ambient thermal resistance <sup>(1)</sup>    | 56.6    | °C AA/ |

| R <sub>θJC (top)</sub> | Junction to case (top) thermal resistance <sup>(1)</sup> | 46.8    | °C/W   |

# **THERMAL INFORMATION (continued)**

| PARAMETER        | THERMAL METRIC                                      | QFN-18L | UNIT |

|------------------|-----------------------------------------------------|---------|------|

| R <sub>θJB</sub> | Junction to board thermal resistance <sup>(1)</sup> | 8.8     | °C/W |

(1) SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT61240 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT61240. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JA}$  and  $R_{\theta JC}$ .

5

## **ELECTRICAL CHARACTERISTICS**

VIN=10V, TA=-40°C~150°C, typical values are tested under 25°C

| SYMBOL                   | PARAMETER                      | TEST CONDITION                                                                                       | MIN | TYP                       | MAX  | UNI |

|--------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|-----|---------------------------|------|-----|

| Power Supply             | y                              |                                                                                                      |     |                           |      |     |

| VIN                      | Operating input voltage        |                                                                                                      | 4   |                           | 19   | V   |

|                          | Input UVLO Rising Threshold    |                                                                                                      | 3.6 | 3.8                       | 3.95 | V   |

| VIN_UVLO                 | Hysteresis                     |                                                                                                      |     | 200                       |      | mV  |

| ISHDN                    | Shutdown current from VIN pin  | EN=0, no load                                                                                        |     | 1                         | 10   | μA  |

| lq                       | Quiescent current from VIN pin | EN=3V, no load, non-switching                                                                        |     | 1                         | 2    | mA  |

| Q_ACTIVE <sup>(1)</sup>  | Quiescent current from VIN pin | EN=3V, no load, switching                                                                            |     | 10                        |      | mA  |

| Enable                   |                                | •                                                                                                    |     |                           |      |     |

| N (                      | EN rising threshold            |                                                                                                      | 1.1 | 1.2                       | 1.3  | V   |

| Ven                      | EN hysteresis                  |                                                                                                      |     | 100                       |      | mV  |

| I <sub>EN</sub>          | EN Pin Input Leakage           | EN=5V, VIN=0V                                                                                        |     | 0.01                      | 1    | μA  |

| Oscillator and           | d Timing                       |                                                                                                      |     |                           |      |     |

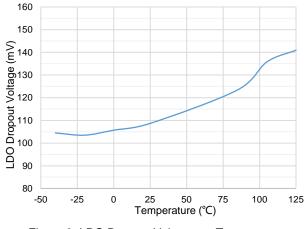

| Fsw                      | Switching Frequency            |                                                                                                      | 2   | 2.2                       | 2.4  | MH  |

|                          | Spread Spectrum range          |                                                                                                      | 4   | 5                         | 6    | %   |

| FSS                      | Spread Spectrum frequency      |                                                                                                      | 3.5 | 4.3                       | 5    | kHz |

| Ton_min                  | Minimum On Time                |                                                                                                      |     | 60                        |      | ns  |

| TOFF_MIN                 | Minimum Off Time               |                                                                                                      |     | 60                        |      | ns  |

| T <sub>SS_BK1</sub>      | BUCK1 soft start time          | $V_{OUT1}$ =3.1V, from 0 to 100%                                                                     |     | 400                       |      | μs  |

| Tss_вк2                  | BUCK2 soft start time          | V <sub>OUT2</sub> =1.8V, from 0 to 100%                                                              |     | 400                       |      | μs  |

| Tss_вкз                  | BUCK3 soft start time          | V <sub>OUT3</sub> =1.2V, from 0 to 100%                                                              |     | 400                       |      | μs  |

| T <sub>SS_LDO</sub>      | LDO soft start time            | V <sub>OUT4</sub> =2.8V, C <sub>NR</sub> =100nF,<br>C <sub>OUT</sub> =10µF, I <sub>LOAD</sub> =100mA |     | 100                       | 300  | μs  |

| TPG_delay <sup>(1)</sup> | PG delay                       | Default setting                                                                                      |     | 3.6                       |      | ms  |

| Thiccup                  | Hiccup time                    |                                                                                                      | 2   | 3.6                       | 5.2  | ms  |

| BUCK1 (HV B              | UCK)                           |                                                                                                      |     |                           |      |     |

|                          |                                | SCT61240                                                                                             |     | 3.3                       |      |     |

| Vout1                    | VOUT1 Output Voltage           | SCT61240-0000                                                                                        |     | V <sub>LDO</sub> +0.<br>3 |      | V   |

|                          |                                | SCT61240-0001                                                                                        |     | V <sub>LDO</sub> +0.<br>5 |      | 1   |

| Vout1_acc                | VOUT1 Accuracy                 |                                                                                                      | -2  |                           | 2    | %   |

| Rds_h_bk1                | High-side MOSFET on-resistance | V <sub>BST1</sub> -V <sub>SW1</sub> =5V                                                              |     | 175                       | 350  | mΩ  |

| RDS_L_BK1                | Low-side MOSFET on-resistance  | VIN>5V                                                                                               |     | 75                        | 150  | mΩ  |

| Low-side MOSFET on-resistance     | VIN>5V                                                                                                                                |                                                       | 75                                                                                                                                                                                                                                                                                                                                                          | 150                                                                                                                                                                                                                                                                                                                                                                                                                                          | mΩ                                                      |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| SW1 HS Switch Lookage Current     | T <sub>A</sub> =25°C                                                                                                                  |                                                       | 0.01                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                            | μA                                                      |

| SWI HS Switch Leakage Current     | T <sub>A</sub> =-40°C~150°C                                                                                                           |                                                       | 1                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                              | μA                                                      |

| SW(1   S Switch   colvege Current | T <sub>A</sub> =25°C                                                                                                                  |                                                       | 0.01                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                            | μA                                                      |

| Swir LS Switch Leakage Current    | T <sub>A</sub> =-40°C~150°C                                                                                                           |                                                       | 4                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                              | μA                                                      |

| Peak Current Limit                |                                                                                                                                       | 1.6                                                   | 2                                                                                                                                                                                                                                                                                                                                                           | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                          | А                                                       |

| Valley Current Limit              |                                                                                                                                       | 1.4                                                   | 1.8                                                                                                                                                                                                                                                                                                                                                         | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                          | А                                                       |

| Reverse Current Limit             |                                                                                                                                       | 0.9                                                   | 1.3                                                                                                                                                                                                                                                                                                                                                         | 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                          | А                                                       |

| VOUT1 PIN Leakage                 | VIN=EN=0V                                                                                                                             |                                                       | 100                                                                                                                                                                                                                                                                                                                                                         | 150                                                                                                                                                                                                                                                                                                                                                                                                                                          | μA                                                      |

|                                   | SW1 HS Switch Leakage Current<br>SW1 LS Switch Leakage Current<br>Peak Current Limit<br>Valley Current Limit<br>Reverse Current Limit | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ | $\begin{tabular}{ c c c c c } \hline T_A=25^\circ C & $$T_A=-40^\circ C \sim 150^\circ C$ \\ \hline T_A=-40^\circ C \sim 150^\circ C$ \\ \hline T_A=25^\circ C & $$T_A=-40^\circ C \sim 150^\circ C$ \\ \hline \hline Peak Current Limit & $$1.6$ \\ \hline Valley Current Limit & $$1.4$ \\ \hline Reverse Current Limit & $$0.9$ \\ \hline \end{tabular}$ | $ \begin{array}{c c} & T_{A}=25^{\circ}\text{C} & 0.01 \\ \hline T_{A}=-40^{\circ}\text{C}\sim150^{\circ}\text{C} & 1 \\ \hline T_{A}=-25^{\circ}\text{C} & 0.01 \\ \hline T_{A}=-25^{\circ}\text{C} & 0.01 \\ \hline T_{A}=-40^{\circ}\text{C}\sim150^{\circ}\text{C} & 4 \\ \hline Peak \ Current \ Limit & 1.6 & 2 \\ \hline Valley \ Current \ Limit & 1.4 & 1.8 \\ \hline Reverse \ Current \ Limit & 0.9 & 1.3 \\ \hline \end{array} $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

# **ELECTRICAL CHARACTERISTICS (continued)** VIN=10V, TA=-40°C~150°C, typical values are tested under 25°C

| SYMBOL                | PARAMETER                            | TEST CONDITION              | MIN  | TYP                         | MAX  | UNI |

|-----------------------|--------------------------------------|-----------------------------|------|-----------------------------|------|-----|

| RDIS_BUCK1            | VOUT1 Output Discharge<br>resistance |                             | 30   | 50                          | 70   | Ohm |

| BUCK2 (LV BU          | JCK)                                 |                             |      |                             |      |     |

| V <sub>IN23</sub>     | VIN23 Input Voltage Range            |                             | 2.7  |                             | 5    | V   |

| V <sub>OUT2</sub>     | VOUT2 Output Voltage                 |                             |      | 1.8                         |      | V   |

| V <sub>OUT2_ACC</sub> | VOUT2 Accuracy                       |                             | -2   |                             | 2    | %   |

| Rds_h_bk2             | High-side MOSFET on-resistance       | Vout1=3.1V                  |      | 155                         | 260  | mΩ  |

| Rds_l_bk2             | Low-side MOSFET on-resistance        | VIN>5V                      |      | 75                          | 125  | mΩ  |

|                       |                                      | T <sub>A</sub> =25°C        |      | 0.01                        | 1    | μA  |

| IILEAK_HS_BUCK2       | SW2 HS Switch Leakage Current        | T <sub>A</sub> =-40°C~150°C |      | 7                           |      | μA  |

| IILEAK_LS_BUCK2       | SW2 LS Switch Leakage Current        |                             |      | 0.01                        | 1    | μA  |

| PEAK_BUCK2            | Peak Current Limit                   |                             | 0.9  | 1.2                         | 1.65 | А   |

| VALLEY_BUCK2          | Valley Current Limit                 |                             | 0.65 | 1                           | 1.3  | А   |

| REVERSE_BUCK2         | Reverse Current Limit                |                             | 0.4  | 0.7                         | 1    | А   |

| IILEAK_VOUT2          | VOUT2 PIN Leakage                    |                             |      | 1                           | 10   | μA  |

| RDIS_BUCK2            | VOUT2 Output Discharge resistance    |                             | 30   | 50                          | 70   | Ohm |

| BUCK3 (LV BU          | JCK)                                 |                             |      |                             |      |     |

| V <sub>IN23</sub>     | VIN23 Input Voltage Range            |                             | 2.7  |                             | 5    | V   |

| Vout3                 | VOUT3 Output Voltage                 |                             |      | 1.1/<br>1.2/<br>1.3/<br>1.5 |      | V   |

| Vout3_acc             | VOUT3 Accuracy                       |                             | -2   |                             | 2    | %   |

| Rds_н_вкз             | High-side MOSFET on-resistance       | Vout1=3.1V                  |      | 155                         | 260  | mΩ  |

| Rds_l_bk3             | Low-side MOSFET on-resistance        | VIN>5V                      |      | 75                          | 125  | mΩ  |

|                       |                                      | T <sub>A</sub> =25°C        |      | 0.01                        | 1    | μA  |

| IILEAK_HS_BUCK3       | SW3 HS Switch Leakage Current        | T <sub>A</sub> =-40°C~150°C |      | 7                           |      | μA  |

| IILEAK_LS_BUCK3       | SW3 LS Switch Leakage Current        |                             |      | 0.01                        | 1    | μA  |

| PEAK_BUCK3            | Peak Current Limit                   |                             | 1.45 | 2                           | 2.75 | Α   |

| VALLEY_BUCK3          | Valley Current Limit                 |                             | 1.15 | 1.7                         | 2.15 | Α   |

| REVERSE_BUCK3         | Reverse Current Limit                |                             | 0.4  | 0.7                         | 1    | Α   |

| IILEAK_VOUT3          | VOUT3 PIN Leakage                    |                             |      | 1                           | 10   | μA  |

| Rdis_buck3            | VOUT3 Output Discharge resistance    |                             | 30   | 50                          | 70   | Ohm |

| LDO                   |                                      |                             |      | 1                           |      | 1   |

|                       | LDOIN Input Voltage Range            |                             | 2.7  |                             | 5    | V   |

| VLDOIN                | == ent inpat tenage trange           |                             |      |                             | 1    | 1   |

| V <sub>LDOIN</sub>    | LDO Output Voltage                   |                             |      | 2.7/<br>2.8/<br>2.9/<br>3.3 |      | v   |

# **ELECTRICAL CHARACTERISTICS (continued)** VIN=10V, TA=-40°C~150°C, typical values are tested under 25°C.

| SYMBOL                     | PARAMETER                                                  | TEST CONDITION                                                                               | MIN      | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------|------|------|------|

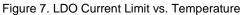

| Vdrop_ldo                  | LDO Dropout Voltage                                        | LDOIN=2.9V, setting LDO<br>output =2.8V, ILDO = 300mA                                        |          | 110  | 200  | mV   |

| LDO_LINE_REG               | LDO Line Regulation                                        | LDOOUT set to 2.7V,<br>LDOIN=3V to 5V, ILDO =<br>100mA                                       |          | 0.02 |      | %/V  |

| LDO_LOAD_REG               | LDO Load Regulation                                        | LDOIN=3.3V, LDOOUT=2.7V,<br>ILDO from 10mA to 300mA.                                         |          | 0.03 |      | %    |

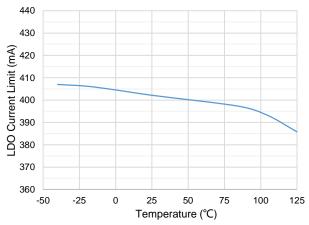

|                            | LDO Current Limit                                          | LDOIN=3 V, setting LDOOUT<br>to 2.8V, force LDOOUT=2.5V                                      | 350      | 400  | 460  | mA   |

|                            |                                                            | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA @ 1kHz                  |          | 70   |      | dB   |

| PSRR_LDO <sup>(1)</sup> LI |                                                            | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA @ 10kHz                 |          | 56   |      | dB   |

|                            | LDO PSRR                                                   | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA @ 100kHz                |          | 35   |      | dB   |

|                            |                                                            | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA @ 1MHz                  |          | 29   |      | dB   |

|                            |                                                            | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA @ 2.2MHz                |          | 24   |      | dB   |

| eN_ldo <sup>(1)</sup>      | LDO noise                                                  | LDOIN= 3.1V, LDOOUT=2.8V,<br>C(NR)=100nF, COUT=20µF,<br>ILDO = 100mA,<br>From 10Hz to 100kHz |          | 30   |      | μVrm |

| ILEAK_LDOOUT               | LDOOUT(VOUT4) PIN Leakage                                  |                                                                                              |          | 0.01 | 1    | μA   |

| R <sub>DIS_LDO</sub>       | LDOOUT(VOUT4) Output<br>Discharge resistance               |                                                                                              | 30       | 50   | 70   | Ohm  |

| Power Good                 | OV/UV threshold                                            |                                                                                              |          |      |      |      |

| PGOV                       | Vout1/2/3/4 Power Good Over<br>Voltage Threshold, Rising   |                                                                                              | 105      | 110  | 115  | %    |

|                            | Hysteresis                                                 |                                                                                              |          | 2.5  |      | %    |

| PGUV                       | Vout1/2/3/4 Power Good Under<br>Voltage Threshold, Falling |                                                                                              | 85       | 90   | 95   | %    |

|                            | Hysteresis                                                 |                                                                                              |          | 2.5  |      | %    |

| Protection                 |                                                            |                                                                                              |          |      |      |      |

| Vout,ovp                   | Vout1/2/3/4 Over Voltage Threshold,<br>Rising              |                                                                                              | 115      | 120  | 125  | %    |

|                            | Hysteresis                                                 |                                                                                              |          | 5    |      | %    |

| Vout,uvp                   | Vout1/2/3/4 Under Voltage<br>Threshold, Falling            |                                                                                              | 70       | 75   | 80   | %    |

|                            | Hysteresis                                                 |                                                                                              | <u> </u> | 5    |      | %    |

| Vin,ovp                    | VIN Over Voltage Threshold, Rising                         |                                                                                              | 19.5     | 21   | 22.5 | V    |

| .,                         | Hysteresis                                                 |                                                                                              |          | 1    |      | V    |

|                            | Thermal shutdown threshold, Rising                         |                                                                                              |          | 175  |      | °C   |

| T <sub>SD</sub>            | Hysteresis                                                 |                                                                                              |          | 15   |      | °C   |

(1) Guaranteed by design and bench, not test in production.

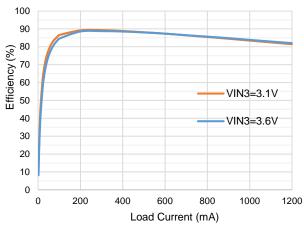

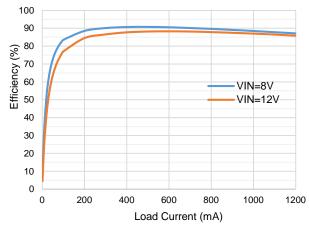

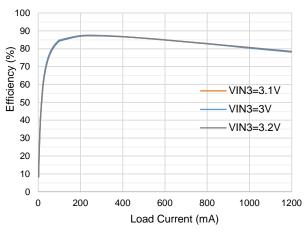

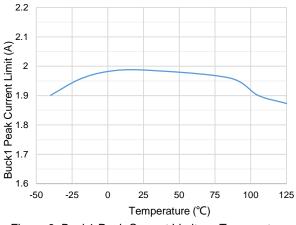

## **TYPICAL CHARACTERISTICS**

$V_{IN}=10V$ ,  $T_A=-40^{\circ}C\sim125^{\circ}C$ , unless otherwise noted.

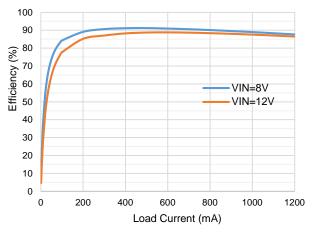

Figure 1. Buck1 Efficiency vs Load Current, V<sub>OUT1</sub>=3.2V

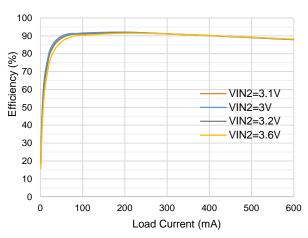

Figure 3. Buck2 Efficiency vs. Load Current, VOUT2=1.8V

Figure 5. Buck3 Efficiency vs. Load Current, VOUT3=1.5V

Figure 2. Buck1 Efficiency vs Load Current, Vout1=3.0V

Figure 4. Buck3 Efficiency vs. Load Current, V<sub>OUT3</sub>=1.2V

Figure 6. Buck1 Peak Current Limit vs. Temperature

# TYPICAL CHARACTERISTICS (continued) $V_{IN}=10V$ , $T_A=-40^{\circ}C\sim125^{\circ}C$ , unless otherwise noted.

Figure 9. LDO Dropout Voltage vs. Temperature, ILDO=300mA

Figure 8. Switching Frequency vs. Temperature

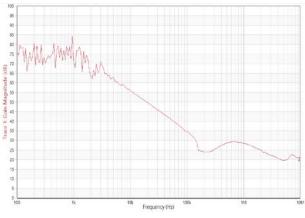

Figure 10. LDO PSRR, ILDO=100mA

9

Figure 11. Functional Block Diagram

## **OPERATION**

#### Overview

The SCT61240 is a highly integrated power management IC (PMIC) optimized for camera system. It integrates three high efficiency synchronous BUCK converters (HVBUCK1, LVBUCK2, LVBUCK3), and a high-PSRR low noise LDO with OV/UV monitoring on all outputs.

VOUT1 is the output of BUCK1, which is powered from VIN (Power Over Coax) and can output 1.2A continuous current with the output voltage set to LDOOUT+300mV/500mV or fixed 3.3V.

VOUT2 is the output of BUCK2, which is powered from VOUT1 and can output 600mA continuous current with the output voltage fixed to 1.8V.

VOUT3 is the output of BUCK3, which is powered from VOUT1 and can output 1.2A continuous current with the output voltage set to 1.1V/1.2V/1.3V/1.5V through RSET PIN for different sensors.

LDOOUT is the output of LDO, which is powered from VOUT1 (need to connect LDOIN to VOUT1) and can output 300mA continuous current with the output voltage set to 2.7V/2.8V/2.9V/3.3V through RSET PIN for different sensors.

With a compact QFN2.5x3.5 package, the SCT61240 greatly reduces external components count and PCB space.

#### VIN and EN UVLO

When the VIN pin voltage rises above 3.8V and the EN pin voltage exceeds the enable threshold of 1.2V, the device is enabled. And the device disables when the VIN pin voltage falls below 3.8V or when the EN pin voltage is below 1.1V.

An internal  $10M\Omega$  resistor pulls EN pin to an internal 5V power supply allows the device to be enabled when EN pin is floating to simplify the system design.

#### **High Efficiency Buck Converters**

All the 3 BUCKs employ 2.2MHz fixed frequency peak current mode control with forced continuous conduction mode (FCCM). Built-in UVLO, soft-start (0.5ms/1ms/1.5ms/2ms options by OTP trim), compensation and hiccup (or latch off option by OTP trim) make the buck converters easily to be used by minimizing the off-chip component count.

For buck1, an external 100nF ceramic bootstrap capacitor between BST and SW1 pin powers high-side power MOSFET gate driver. The bootstrap capacitor voltage is charged from an integrated voltage regulator when high-side power MOSFET is off and low-side power MOSFET is on.

The converters have proprietary designed gate driver scheme to resist switching node ringing without sacrificing MOSFET turn-on and turn-off time, which further erases high frequency radiation EMI noise caused by the MOSFETs hard switching.

The converters implement over current protection with cycle-by-cycle limiting high-side MOSFET peak current and also low-side MOSFET valley current to avoid inductor current running away during unexpected overload and hiccup protection in output hard short condition. When overload or hard short happens, the converter cannot provide output current to satisfy loading requirement even though the inductor current has already been clamped at over current limitation. Thus, output voltage drops below regulated voltage continuously. When output voltage loss regulation lasts for 100 us, the converter stops switching, after remaining OFF for 3.2 ms, the device will attempt to restart. The hiccup protection mode greatly reduces the average short circuit current to alleviate thermal issues and protect the regulator.

#### **Over Voltage Protection**

If an output exceeds the over voltage protection threshold, all outputs will shut off for the hiccup time. When hiccup ends, the normal power up sequence will start again according to the SEQ and RSET setting. When entry hiccup, the output discharge will operate during the hiccup time.

#### **Under Voltage Protection**

If an output falls below the under voltage protection threshold, all outputs will shut off for the hiccup time. When hiccup ends, the normal power up sequence will start again according to the SEQ and RSET setting. When entry hiccup, the output discharge will operate during the hiccup time.

#### Over Current Protection (OCP)

For the three bucks and LDO, the SCT61240 provides both peak and valley current limit designed to limit the peak/valley inductor current to ensure that the switching currents remain within the device capabilities during overload conditions or during an output short circuit.

When the HS-FET turns on, the chip monitors the increased IL through the relevant operating main power switch. Once the peak IL exceeds the peak current limit threshold, the HS-FET turns off immediately, and the LS-FET turns on to conduct and decrease IL. The HS-FET does not turn on again until IL falls below the valley current limit threshold. If the feedback voltage makes EA's output level triggers the high clamp limit consecutively in a settled cycle, an over-current (OC) fault is reported and OCP is activated, all outputs will shut off for the hiccup time. When hiccup ends, the normal power up sequence will start again according to the SEQ and RSET setting.

#### Power Good

The PG pin is a push-pull output. It goes to logic high when the device is powered on, and all outputs are within the power good range, and no faults reported. The high output level can be programmed to either 3.3V or 1.8V.

PG will assert low when any of below events occur:

- Buck1's output is out of power good range or VOUT OV/UV range or OCP

- Buck2's output is out of power good range or VOUT OV/UV range or OCP

- Buck3's output is out of power good range or VOUT OV/UV range or OCP

- LDO's output is out of power good range or VOUT OV/UV range or OCP

- Junction temperature is over Thermal Shutdown point

- VIN is higher than VIN OVP threshold

#### **Hiccup or Latch off Protection**

When below faults are detected, the SCT61240 will enter hiccup or latch off mode (programmable option). When select hiccup mode and entry hiccup, all the channels shut off for 3.2ms, and then the normal power up sequence will start again according to the SEQ and RSET setting. When select latch off mode and entry latch off, all the channels shut off and not restart unless VIN/EN power on reset (POR).

The faults that make the device entry hiccup/latch off protection:

- Buck1's output is out of VOUT OV/UV range or OCP

- Buck2's output is out of VOUT OV/UV range or OCP

- Buck3's output is out of VOUT OV/UV range or OCP

- LDO's output is out of VOUT OV/UV range or OCP

- Junction temperature is over Thermal Shutdown point

- VIN is higher than VIN OVP threshold

#### **Output Discharge**

In order to discharge the energy of output capacitor during power off sequence, all channels have active discharge path from their output to ground. The discharge path is turn-on when channel is disabled.

#### Internal Soft-Start

The soft start function is implemented to prevent the PMIC output voltage from overshooting during start-up. When the PMIC starts up, the internal circuitry of each power rail generates a soft-start voltage that ramps up from 0V. The soft-start period lasts until the voltage on the soft-start capacitor exceeds the reference voltage. At this point,

12 For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved

the reference voltage takes over.

#### Frequency Spread Spectrum

To meet CISPR and EMI compliances, the SCT61240 implements Frequency Spread Spectrum (FSS) function. The FSS circuitry shifts the 2.2MHz switching frequency within ±5% range and 1/512 of the switching frequency periodically. Therefore, the SCT61240 can guarantee that the switching frequency does not drop into the 1.8MHz AM band limit.

#### **Thermal Shutdown**

The SCT61240 protects the device from damage during excessive heat and power dissipation condition. Once the junction temperature exceeds 170C, the thermal sensing circuit disable all channels and enter hiccup or latch off. When the junction temperature falls below 150C and hiccup ends, then the device restarts.

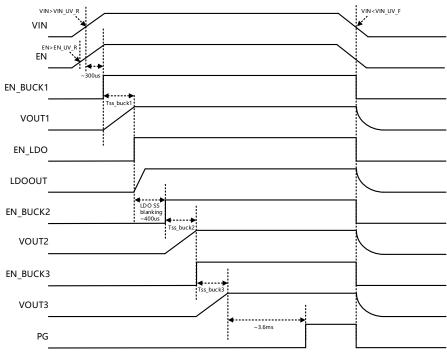

#### **Power on/off Sequence Control**

For power on, the SCT61240 supports 6 power-on sequences for buck2&3 and LDO through SEQ pin. Since the output of BUCK1 is the power for the next three channels, BUCK1 is always set to startup first.

For power off, through VIN/EN or entry hiccup/latch off, all channels power off simultaneously.

Connect a resistor between SEQ and GND to set the power on sequence before enabling the device. The SEQ detection only activated at the beginning of power on, and the sequence configuration is latched once SEQ detection done. When the resistance selected out of range, CH2&CH3&CH4 are disabled. Any change during the power on procedure is not guarantee to the correct power-on sequence.

Below table shows the power-on sequence with its corresponding resistance. CH1 is BUCK1, CH2 is BUCK2, CH3 is BUCK3, CH4 is LDO.

| SEQ No. | SEQ Resistance(Ω) |       |       | Converse |     |     |     |  |

|---------|-------------------|-------|-------|----------|-----|-----|-----|--|

| SEQ NO. | MIN               | TYP   | MAX   | Sequence |     |     |     |  |

| SEQ1    | 0                 | 0     | 3k    | CH1      | CH4 | CH2 | CH3 |  |

| SEQ2    | 6k                | 8k    | 10k   | CH1      | CH2 | CH4 | CH3 |  |

| SEQ3    | 14k               | 16k   | 18k   | CH1      | CH2 | CH3 | CH4 |  |

| SEQ4    | 24k               | 27k   | 30k   | CH1      | CH3 | CH2 | CH4 |  |

| SEQ5    | 40k               | 45.5k | 50k   | CH1      | CH3 | CH4 | CH2 |  |

| SEQ6    | 400k              | Float | Float | CH1      | CH4 | CH3 | CH2 |  |

#### Table 1. Power-On Sequence Control

Figure 12. Example SEQ1 for SCT61240

#### **Output Voltage Setting**

The device provides 9 flexible voltage setting through RSET PIN for various sensors. Connect a resistor between RSET and GND to set the output voltage of each channel before enabling the device. The RSET detection only activated at the beginning of power on, and the output voltage configuration is latched once RSET detection done. Any change during the power on procedure is not guarantee to the correct output voltage setting.

Below table shows the output voltage setting with its corresponding resistance.

| Table 2. Output Voltage Setting |                    |       |       |                   |            |       |       |     |

|---------------------------------|--------------------|-------|-------|-------------------|------------|-------|-------|-----|

|                                 | RSET Resistance(Ω) |       |       | Output voltage(V) |            |       |       |     |

| RSET                            |                    |       |       | BUCK1             | BUCK1      |       |       |     |

| No.                             | MIN                | TYP   | MAX   | (SCT61240-        | (SCT61240- | BUCK2 | BUCK3 | LDO |

|                                 |                    |       |       | 0000)             | 0001)      |       |       |     |

| VSET1                           | 0                  | 0     | 3k    | 3.1               | 3.3        | 1.8   | 1.2   | 2.8 |

| VSET2                           | 6k                 | 8k    | 10k   | 3.0               | 3.2        | 1.8   | 1.2   | 2.7 |

| VSET3                           | 14k                | 16k   | 18k   | 3.1               | 3.3        | 1.8   | 1.1   | 2.8 |

| VSET4                           | 24k                | 27k   | 30k   | 3.1               | 3.3        | 1.8   | 1.5   | 2.8 |

| VSET5                           | 40k                | 45.5k | 50k   | 3.2               | 3.4        | 1.8   | 1.2   | 2.9 |

| VSET6                           | 70k                | 76k   | 90k   | 3.6               | 3.8        | 1.8   | 1.1   | 3.3 |

| VSET7                           | 120k               | 127k  | 140k  | 3.6               | 3.8        | 1.8   | 1.3   | 3.3 |

| VSET8                           | 210k               | 230k  | 250k  | 3.6               | 3.8        | 1.8   | 1.5   | 3.3 |

| VSET9                           | 400k               | Float | Float | 3.2               | 3.4        | 1.8   | 1.1   | 2.9 |

| RSET  | RSET Resistance(Ω) |       |       | Output voltage(V)   |       |       |     |  |

|-------|--------------------|-------|-------|---------------------|-------|-------|-----|--|

| No.   | MIN                | TYP   | MAX   | BUCK1<br>(SCT61240) | BUCK2 | BUCK3 | LDO |  |

| VSET1 | 0                  | 0     | 3k    |                     | 1.8   | 1.2   | 2.8 |  |

| VSET2 | 6k                 | 8k    | 10k   |                     | 1.8   | 1.2   | 2.7 |  |

| VSET3 | 14k                | 16k   | 18k   | 3.3                 | 1.8   | 1.1   | 2.8 |  |

| VSET4 | 24k                | 27k   | 30k   | 3.3                 | 1.8   | 1.5   | 2.8 |  |

| VSET5 | 40k                | 45.5k | 50k   | ]                   | 1.8   | 1.2   | 2.9 |  |

| VSET6 | 400k               | Float | Float |                     | 1.8   | 1.1   | 2.9 |  |

15

## **APPLICATION INFORMATION**

#### **Typical Application**

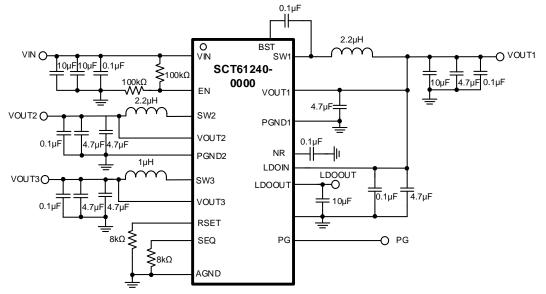

Figure 13. Application Schematic, 4V to 19V, PMIC Regulator at 2.2MHz

| Design Parameters                    |                        |  |  |  |  |

|--------------------------------------|------------------------|--|--|--|--|

| Design Parameters                    | Example Value          |  |  |  |  |

| Input Voltage                        | 10V Normal 4V to 19V   |  |  |  |  |

|                                      | VOUT1: 3.0V            |  |  |  |  |

| Output Valte za                      | VOUT2: 1.8V            |  |  |  |  |

| Output Voltage                       | VOUT3: 1.2V            |  |  |  |  |

|                                      | LDOOUT: 2.7V           |  |  |  |  |

|                                      | VOUT1: 1.2A (in total) |  |  |  |  |

| Maximum Output Current               | VOUT2: 0.6A            |  |  |  |  |

| Maximum Output Current               | VOUT3: 1.2A            |  |  |  |  |

|                                      | LDOOUT: 0.3A           |  |  |  |  |

| Switching Frequency                  | 2.2MHz                 |  |  |  |  |

|                                      | VOUT1: 10mV            |  |  |  |  |

| Output Voltage Ripple (peak to peak) | VOUT2: 2mV             |  |  |  |  |

|                                      | VOUT3: 4mV             |  |  |  |  |

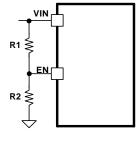

#### Under Voltage Lock-Out

An external voltage divider network of  $R_1$  from the input to EN pin and  $R_2$  from EN pin to the ground can set a higher input voltage's Under Voltage Lock-Out (UVLO) threshold. The UVLO has two thresholds, one for power up when the input voltage is rising and the other for power down or brown outs when the input voltage is falling. Use Equation 1 and Equation 2 to calculate the values of  $R_1$  and  $R_2$  resistors.

$$V_{rise} = \left(1 + \frac{R_1}{R_2}\right) * V_{ENrise} \tag{1}$$

$$V_{fall} = \left(1 + \frac{R_1}{R_2}\right) * V_{ENfall} \tag{2}$$

where

- Vrise is rising threshold of Vin UVLO

- V<sub>fall</sub> is falling threshold of Vin UVLO

- VENrise is rising threshold of EN UVLO

- VENfall is falling threshold of EN UVLO

#### Inductor Selection

Figure 14. System UVLO by enable divide

There are several factors should be considered in selecting inductor such as inductance, saturation current, the RMS current and DC resistance(DCR). Larger inductance results in less inductor current ripple and therefore leads to lower output voltage ripple. However, the larger value inductor always corresponds to a bigger physical size, higher series resistance, and lower saturation current. A good rule for determining the inductance to use is to allow the inductor peak-to-peak ripple current to be approximately 20%~40% of the maximum output current.

The peak-to-peak ripple current in the inductor ILPP can be calculated as in Equation 3.

$$I_{LPP} = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{V_{IN} * L * f_{SW}}$$

(3)

Where

- ILPP is the inductor peak-to-peak current

- L is the inductance of inductor

- fsw is the switching frequency

- VOUT is the output voltage

- V<sub>IN</sub> is the input voltage

Since the inductor-current ripple increases with the input voltage, so the maximum input voltage in application is always used to calculate the minimum inductance required. Use Equation 4 to calculate the inductance value.

$$L_{MIN} = \frac{V_{OUT}}{f_{SW} * LIR * I_{OUT(max)}} * (1 - \frac{V_{OUT}}{V_{IN(max)}})$$

(4)

Where

- L<sub>MIN</sub> is the minimum inductance required

- f<sub>sw</sub> is the switching frequency

- VOUT is the output voltage

- V<sub>IN(max)</sub> is the maximum input voltage

- I<sub>OUT(max)</sub> is the maximum DC load current

- LIR is coefficient of ILPP to IOUT

The total current flowing through the inductor is the inductor ripple current plus the output current. When selecting an inductor, choose its rated current especially the saturation current larger than its peak operation current and RMS current also not be exceeded. Therefore, the peak switching current of inductor, I<sub>LPEAK</sub> and I<sub>LRMS</sub> can be calculated as in equation 5 and equation 6.

$$I_{LPEAK} = I_{OUT} + \frac{I_{LPP}}{2}$$

$$I_{LRMS} = \sqrt{(I_{OUT})^2 + \frac{1}{12} * (I_{LPP})^2}$$

(6)

Where

- ILPEAK is the inductor peak current

- IOUT is the DC load current

- ILPP is the inductor peak-to-peak current

- I<sub>LRMS</sub> is the inductor RMS current

In overloading or load transient conditions, the inductor peak current can increase up to the switch current limit of the device. The most conservative approach is to choose an inductor with a saturation current rating greater than peak current limit. Because of the maximum I<sub>LPEAK</sub> limited by device, the maximum output current that the SCT61240 can deliver also depends on the inductor current ripple. Thus, the maximum desired output current also affects the selection of inductance. The smaller inductor results in larger inductor current ripple leading to a lower maximum output current.

#### Input Capacitor Selection

The input current to the step-down DCDC converter is discontinuous, therefore it requires a capacitor to supply the AC current to the step-down DCDC converter while maintaining the DC input voltage. Use capacitors with low ESR for better performance. Ceramic capacitors with X5R or X7R dielectrics are usually suggested because of their low ESR and small temperature coefficients, and it is strongly recommended to use another lower value capacitor (e.g. 0.1uF) with small package size (0603) to filter high frequency switching noise. Place the small size capacitor as close to VIN and GND pins as possible.

The voltage rating of the input capacitor must be greater than the maximum input voltage. And the capacitor must also have a ripple current rating greater than the maximum input current ripple. The RMS current in the input capacitor can be calculated using Equation 7.

$$I_{CINRMS} = I_{OUT} * \sqrt{\frac{V_{OUT}}{V_{IN}} * (1 - \frac{V_{OUT}}{V_{IN}})}$$

(7)

The worst case condition occurs at  $V_{IN}=2^*V_{OUT}$ , where:

$$I_{\text{CINRMS}} = 0.5 * I_{\text{OUT}} \tag{8}$$

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

When selecting ceramic capacitors, it needs to consider the effective value of a capacitor decreasing as the DC bias voltage across a capacitor increasing.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using Equation 9 and the maximum input voltage ripple occurs at 50% duty cycle.

$$\Delta V_{\rm IN} = \frac{I_{\rm OUT}}{f_{\rm SW} * C_{\rm IN}} * \frac{V_{\rm OUT}}{V_{\rm IN}} * (1 - \frac{V_{\rm OUT}}{V_{\rm IN}})$$

(9)

For this example, two 10µF, X7R ceramic capacitors rated for 50V in parallel are used. And a 0.1 µF for high-frequency filtering capacitor is placed as close as possible to the device pins.

#### **Bootstrap Capacitor Selection**

A 0.1µF ceramic capacitor must be connected between BOOT pin and SW pin for proper operation. A ceramic capacitor with X5R or better grade dielectric is recommended. The capacitor should have a 10V or higher voltage rating.

#### **Output Capacitor Selection**

The selection of output capacitor will affect output voltage ripple in steady state and load transient performance.

The output ripple is essentially composed of two parts. One is caused by the inductor current ripple going through the Equivalent Series Resistance ESR of the output capacitors and the other is caused by the inductor current ripple charging and discharging the output capacitors. To achieve small output voltage ripple, choose a low-ESR output capacitor like ceramic capacitor. For ceramic capacitors, the capacitance dominates the output ripple. For simplification, the output voltage ripple can be estimated by Equation 10 desired.

$$\Delta V_{OUT} = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{8 * f_{SW}^2 * L * C_{OUT} * V_{IN}}$$

(10)

Where

- $\Delta V_{OUT}$  is the output voltage ripple

- fsw is the switching frequency

- L is the inductance of inductor

- COUT is the output capacitance

- VOUT is the output voltage

- V<sub>IN</sub> is the input voltage

Due to capacitor's degrading under DC bias, the bias voltage can significantly reduce capacitance. Ceramic capacitors can lose most of their capacitance at rated voltage. Therefore, leave margin on the voltage rating to ensure adequate effective capacitance. Typically, two  $4.7\mu$ F ceramic output capacitors work for most applications. The LDO is specifically designed to work with a standard ceramic output capacitor to save space and improve performance. Larger output capacitors will improve load transient response and reduce noise at the cost of increased size. A 1 $\mu$ F to 20 $\mu$ F output capacitor should be placed to get stable output.

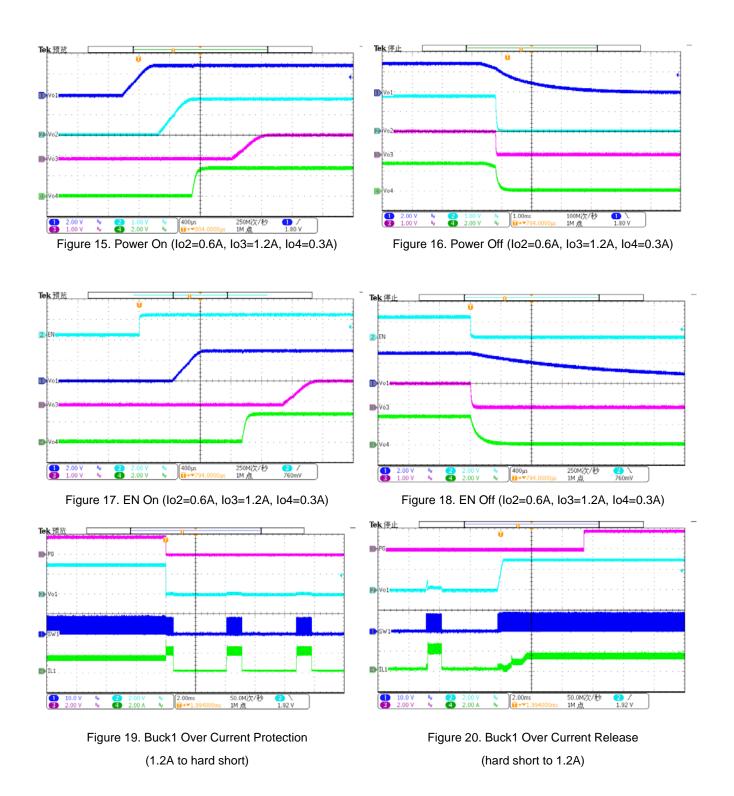

### **Application Waveforms**

Vin=10V, RSET=SEQ=8kΩ, Vout1=3.0V, Vout2=1.8V, Vout3=1.2V, Vout4=2.7V, unless otherwise noted

For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved Product Folder Links: SCT61240

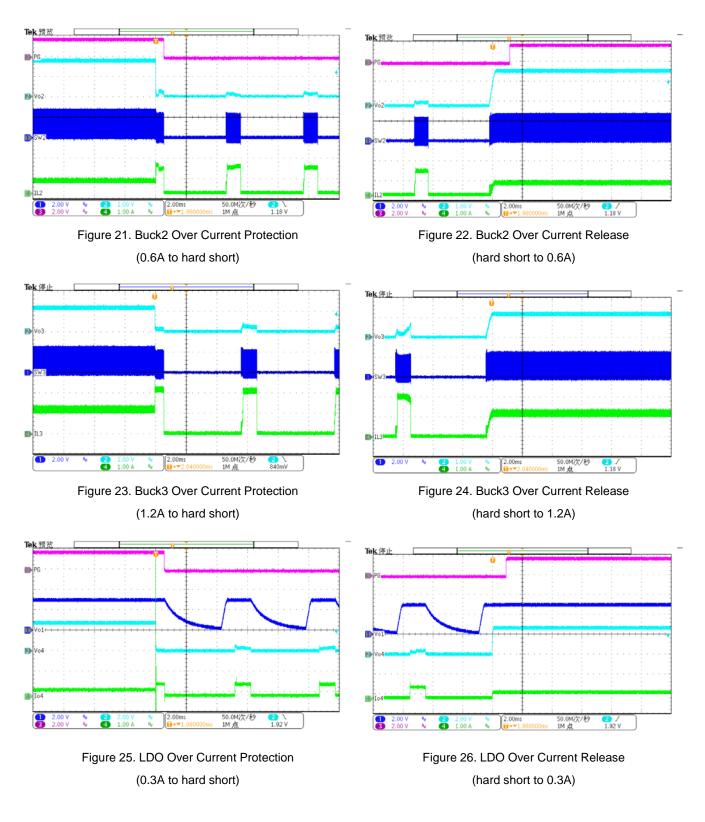

## **Application Waveforms (continued)**

Vin=10V, RSET=SEQ=8kΩ, Vout1=3.0V, Vout2=1.8V, Vout3=1.2V, Vout4=2.7V, unless otherwise noted

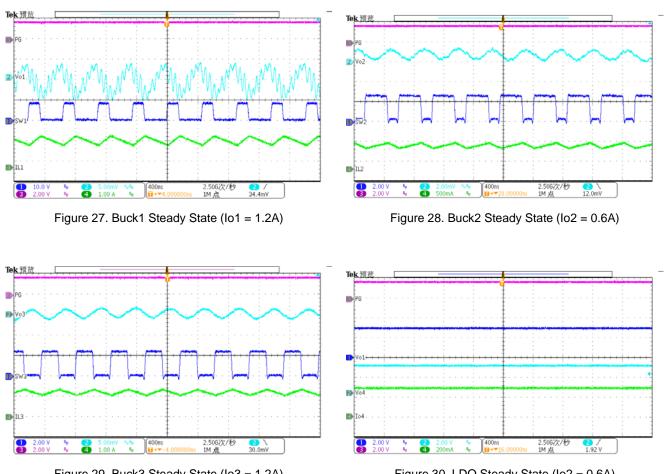

## **Application Waveforms (continued)**

Vin=10V, RSET=SEQ=8kQ, Vout1=3.0V, Vout2=1.8V, Vout3=1.2V, Vout4=2.7V, unless otherwise noted

Figure 29. Buck3 Steady State (Io3 = 1.2A)

Figure 30. LDO Steady State (Io2 = 0.6A)

#### Layout Guideline

Proper PCB layout is a critical for SCT61240's stable and efficient operation. The traces conducting fast switching currents or voltages are easy to interact with stray inductance and parasitic capacitance to generate noise and degrade performance. For better results, follow these guidelines as below:

1. Power grounding scheme is very critical because of carrying power, thermal, and glitch/bouncing noise associated with clock frequency. The thumb of rule is to make ground trace lowest impendence and power are distributed evenly on PCB. Sufficiently placing ground area will optimize thermal and not causing over heat area.

2. Place a low ESR ceramic capacitor as close to VIN pin and the ground as possible to reduce parasitic effect.

3. For operation at full rated load, the top side ground area must provide adequate heat dissipating area. Make sure top switching loop with power have lower impendence of grounding.

4. The bottom layer is a large ground plane connected to the ground plane on top layer by vias. The power pad should be connected to bottom PCB ground planes using multiple vias.

5. Output inductor should be placed close to the SW pin. The switching area of the PCB conductor minimized to prevent excessive capacitive coupling.

6. UVLO adjust resistors and feedback trace should connect to small signal ground which must return to the GND pin without any interleaving with power ground.

7. For LDO low noise area, place an independent copper plane with AGND pin. Use this quiet AGND through LDO power path and sensitive pins NR, RSET, SEQ. To avoid noise interference, using vias to connect AGND to PGND with single point.

8. For achieving better thermal performance, a four-layer layout is strongly recommended.

Figure 31. PCB Layout Example

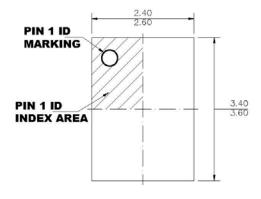

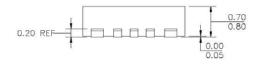

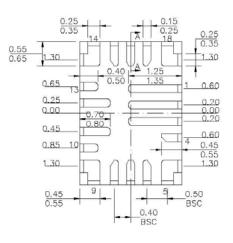

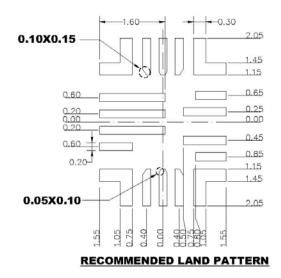

## PACKAGE INFORMATION

SIDE VIEW

BOTTOM VIEW

SECTION A-A

#### NOTE:

THE LEAD SIDE IS WETTABLE.

ALL DIMENSIONS ARE IN MILLIMETERS.

LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

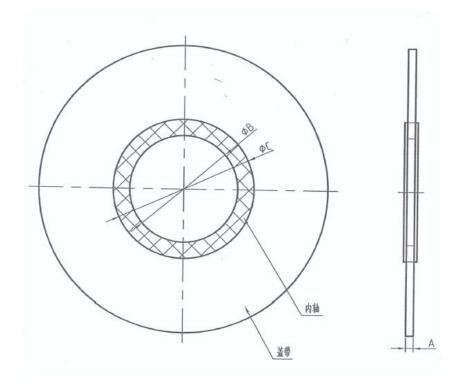

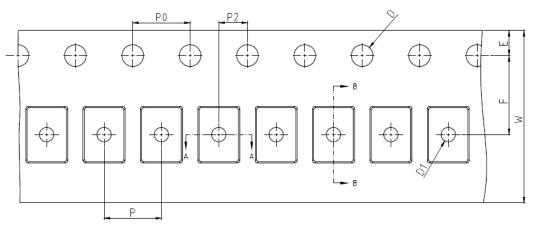

# TAPE AND REEL INFORMATION

| Туре     | A <sub>0</sub> <sup>+0.1</sup> mm | Carrier Width | Diameter           |

|----------|-----------------------------------|---------------|--------------------|

| PRA、F4DK | 9.3                               | 12            |                    |

| HST      | 9.5                               | 12            |                    |

| HST      | 13.5                              | 16            | B=76.2±0.10mm      |

| HST、C800 | 21.3                              | 24            | $C=92.2\pm0.25$ mm |

| 2420S    | 13.3                              | 16            | 0=02.2±0.2011111   |

| 2420S    | 21.3                              | 24            |                    |

| TIST300  | 9.9                               | 12            |                    |

| Symbol | Dimensions in Millimeters    |

|--------|------------------------------|

| A0     | 2.75±0.10                    |

| B0     | 3.75±0.10                    |

| D      | <b>1.5</b> <sup>+0.10</sup>  |

| D1     | 1.00±0.10                    |

| E      | 1.75±0.10                    |

| F      | 5.50±0.05                    |

| K0     | 1.00±0.10                    |

| Р      | 4.00±0.10                    |

| P0     | 4.00±0.10                    |

| P2     | 2.00±0.05                    |

| t      | 0.25±0.03                    |

| W      | 12.00 <sup>+0.30</sup> -0.10 |

| θ      | 5° max                       |